Product Summary

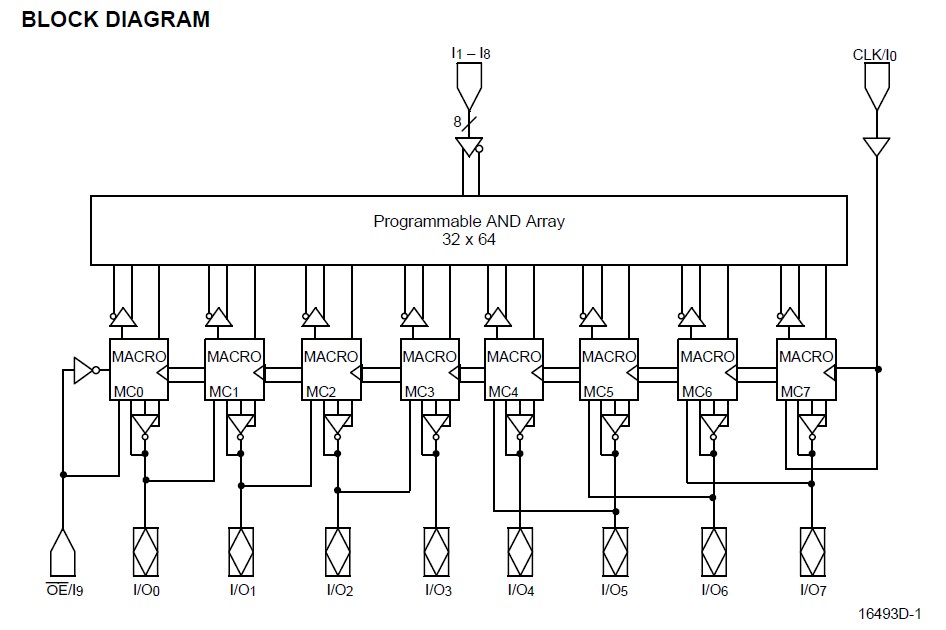

The PALCE16V8Q-25PC is an advanced PAL device built with low-power, high-speed, electrically-erasable CMOS technology. It is functionally compatible with all 20-pin GAL devices. The macrocells provide a universal device architecture. The PALCE16V8Q-25PC will directly replace the PAL16R8 and PAL10H8 series devices, with the exception of the PAL16C1. The PALCE16V8Q-25PC utilizes the familiar sum-of-products (AND/OR) architecture that allows users to implement complex logic functions easily and efficiently. Multiple levels of combinatorial logic can always be reduced to sum-of-products form, taking advantage of the very wide input gates available in PAL devices. The equations are programmed into the device through floatinggate cells in the AND logic array that can be erased electrically.

Parametrics

PALCE16V8Q-25PC absolute maximum ratings: (1)Storage Temperature: –65℃ to +150℃; (2)Ambient Temperature with Power Applied: –55℃ to +125℃; (3)Supply Voltage with Respect to Ground: –0.5 V to + 7.0 V; (4)DC Input Voltage: –0.5 V to VCC + 0.5 V; (5)DC Output or I/O Pin Voltage: –0.5 V to VCC + 0.5 V; (6)Static Discharge Voltage: 2001 V; (7)Latchup Current (TA = –40℃ to +85℃): 100 mA.

Features

PALCE16V8Q-25PC features: (1)Piand functiocompatible with all 20-piGAL devices; (2)Electrically erasable CMOS technology provides reconfigurable logic and full testability; (3)High-speed CMOS technology; (4)Direct plug-ireplacement for the PAL16R8 series and most of the PAL10H8 series; (5)Outputs programmable as registered or combinatorial iany combination; (6)Peripheral Component Interconnect (PCI) compliant; (7)Programmable output polarity; (8)Programmable enable/disable control; (9)Preloadable output registers for testability; (10)Automatic register reset opower up; (11)Cost-effective 20-piplastic DIP, PLCC, and SOIC packages; (12)Extensive third-party software and programmer support through FusionPLD partners; (13)Fully tested for 100% programming and functional yields and high reliability; (14)5 ns versioutilizes a split leadframe for improved performance.

Diagrams

|

PALC16L8 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC16R4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC16R6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC16R8 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC22V10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC22V10-25PC |

|

IC SPLD 10MACROCELL 25NS 24-DIP |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))